Case studies

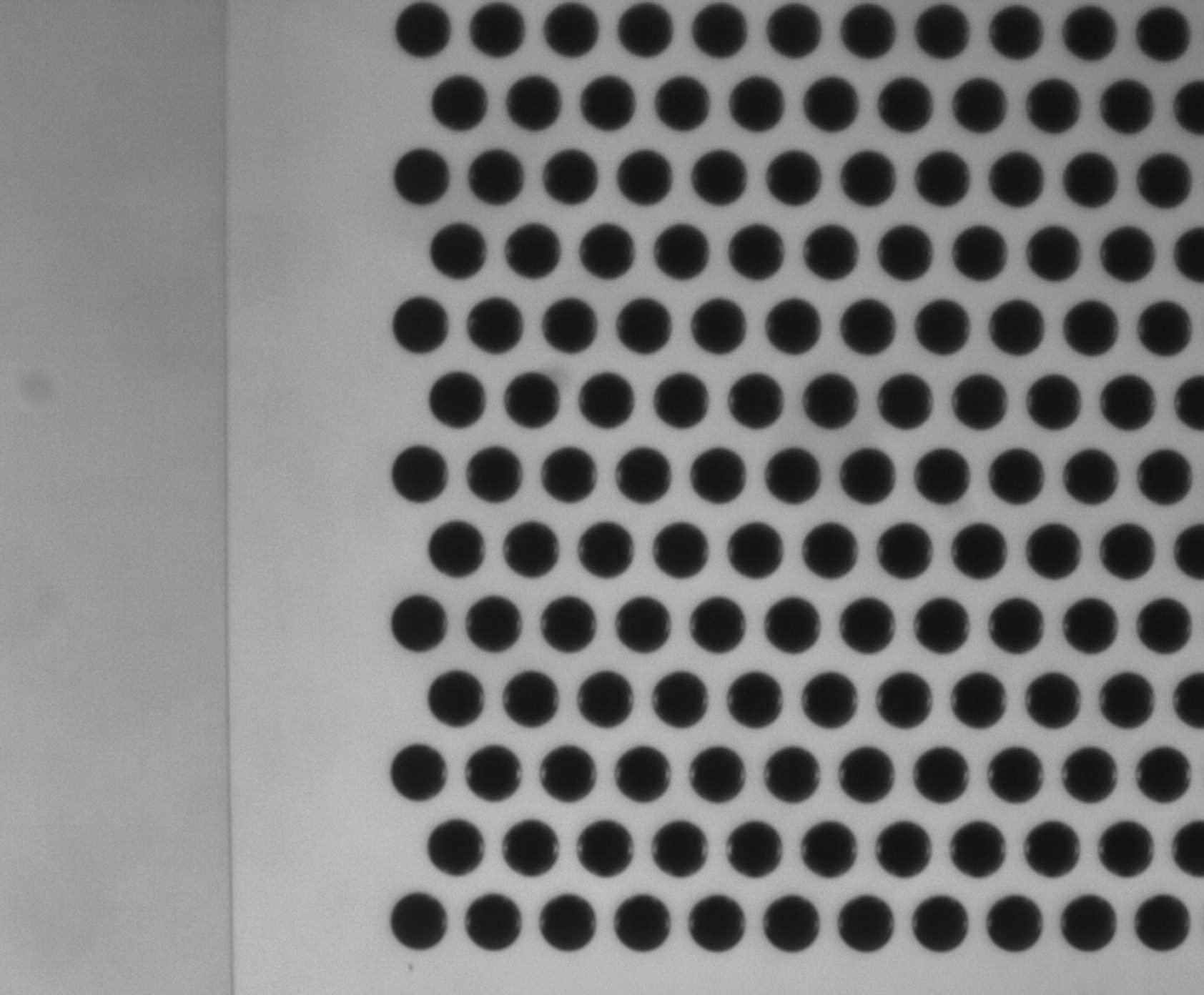

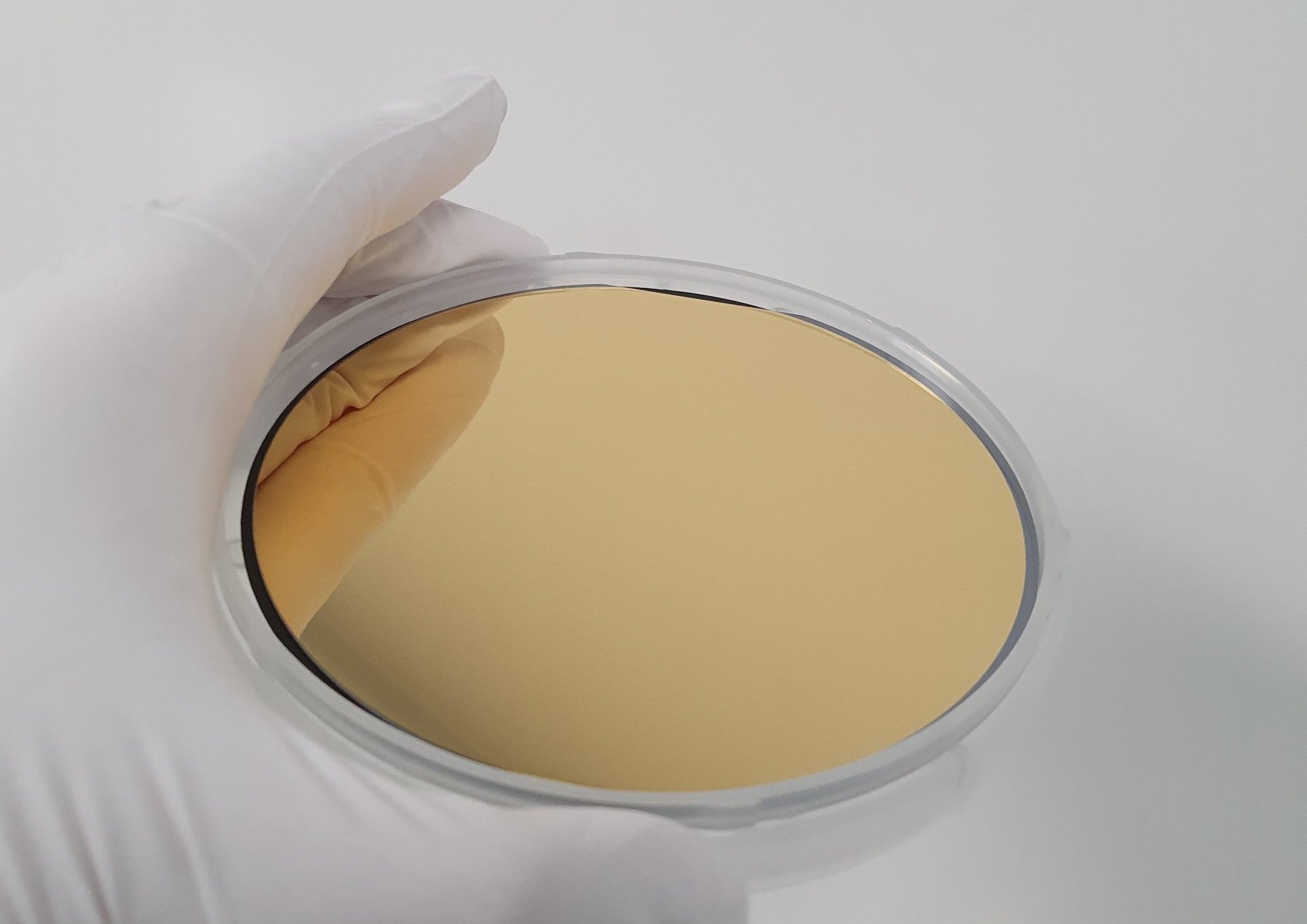

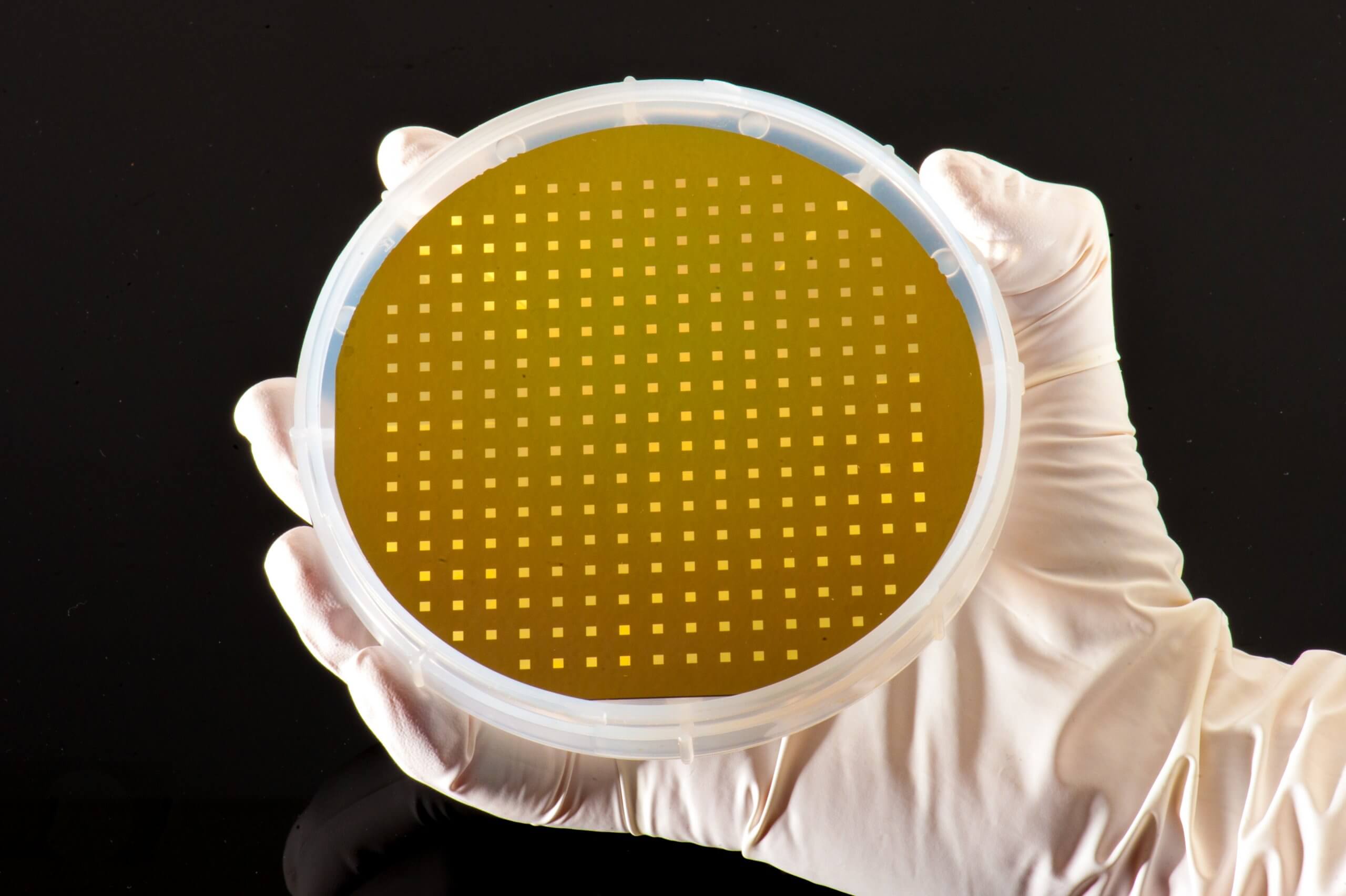

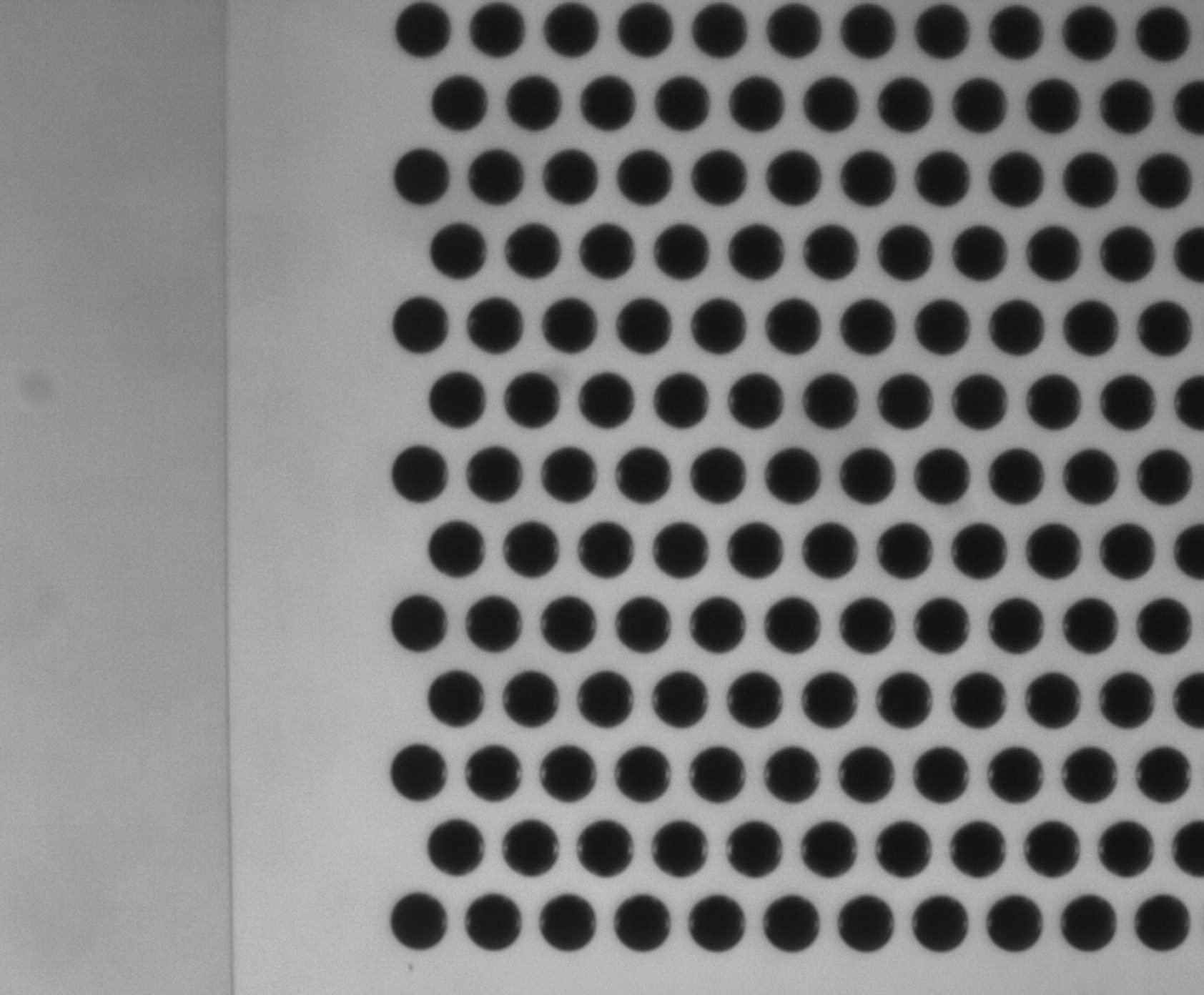

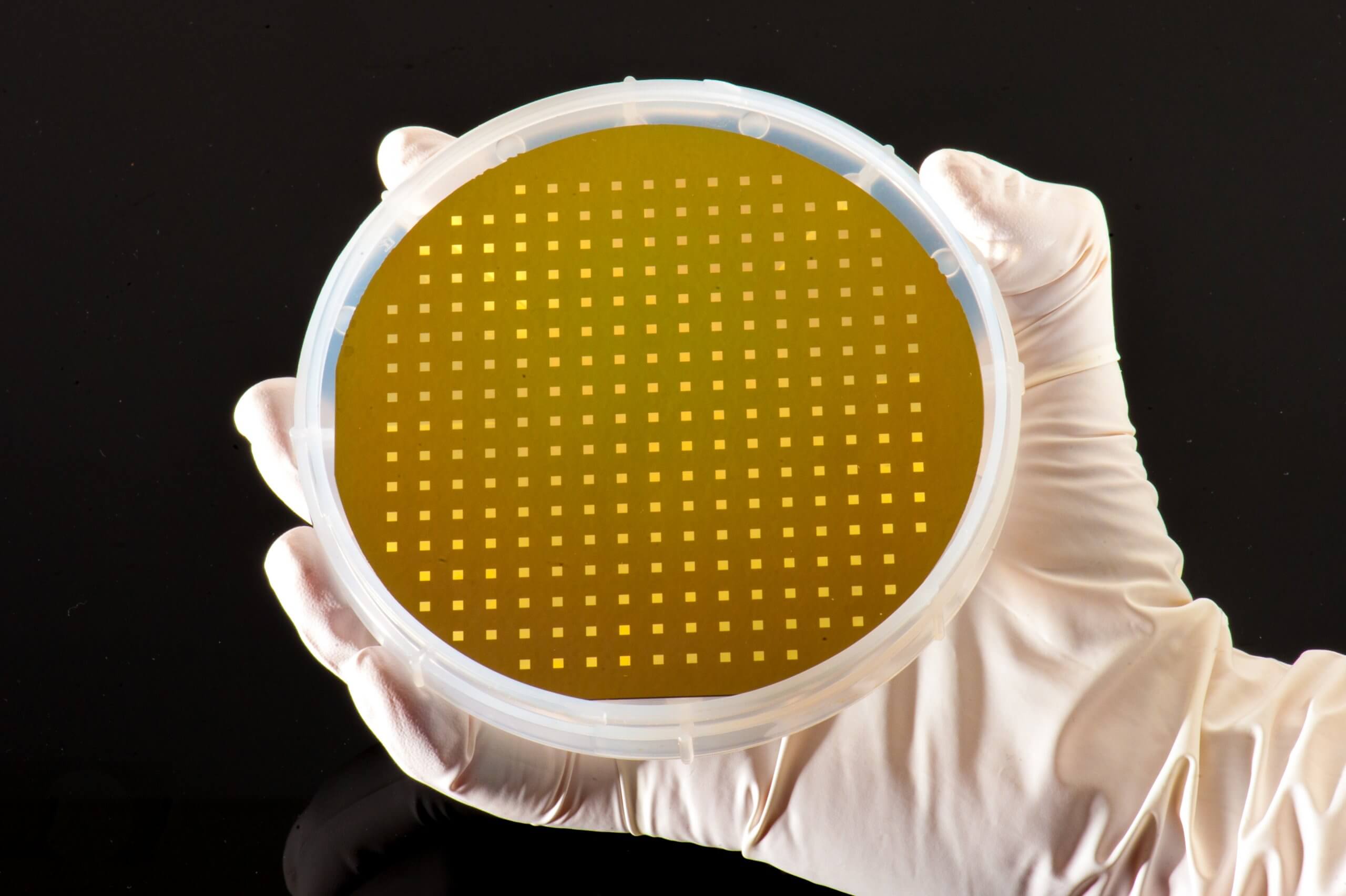

Micro and Nano Engineering have published an article by Sahoo et Al about EUV interference lithography. The introduction reads: “recently, various lithography methods were developed to increase integration levels as well as microchips performance metrics by reducing the dimension of active components, thereby strengthening recent advances in modern semiconductor technology”.

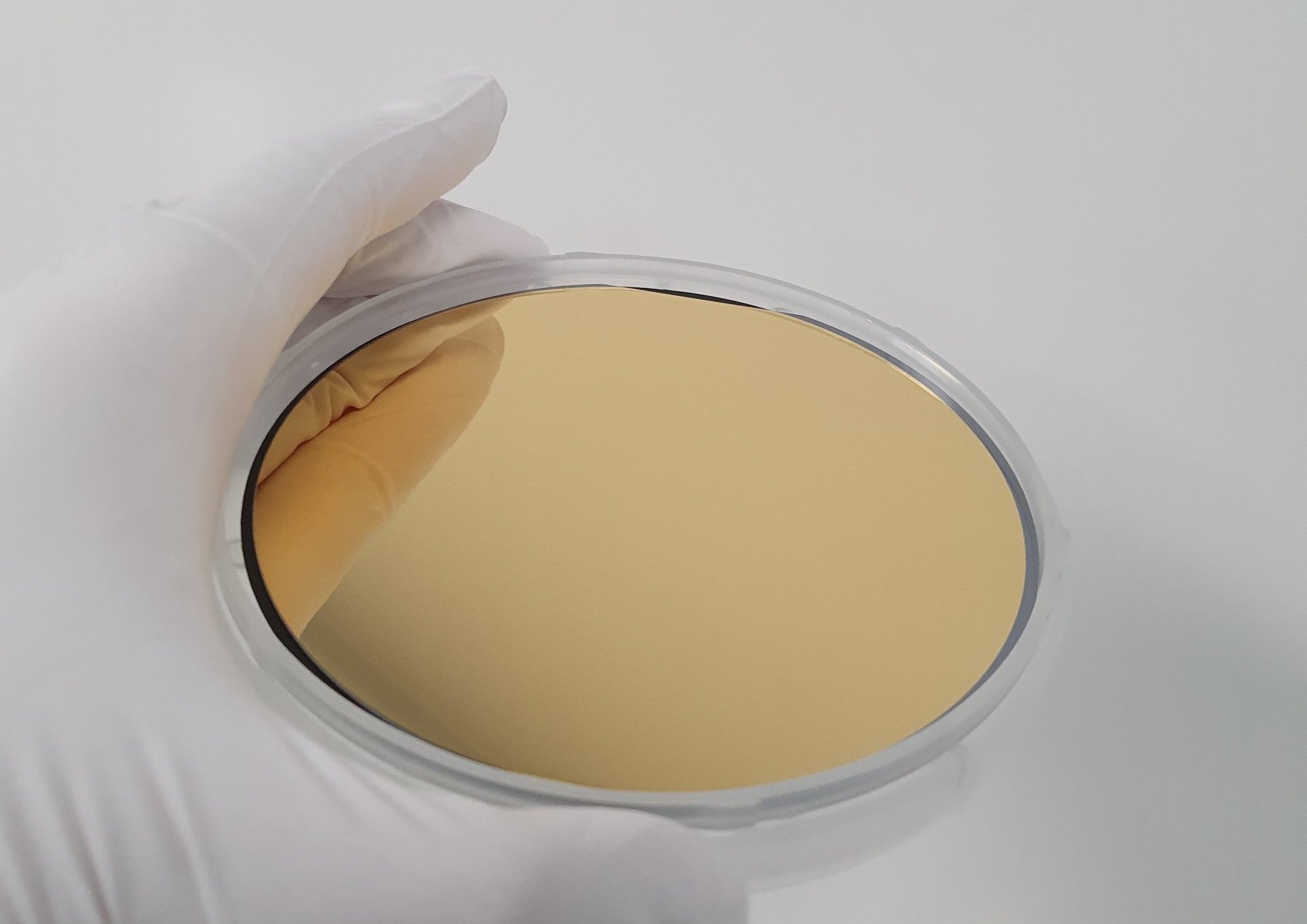

Silson’s silicon nitride membranes were used for the experiments which were performed at Taiwan Light Source 21B2 EUV beamline in the National Synchrotron Radiation Research Center (NSRRC).

Follow this link to read more about the research in full!